基于proteus的计数器设计

计数器原理

由逻辑门构成的电路称为 组合逻辑电路 ,其任何时刻输出端的信号仅取决于该时刻输入端的信号组合,而与输入/输出端原有的状态无关。相对应的,由触发器构成的电路称为时序逻辑电路,其输出不仅是输入信号的组合,还是电路当前状态的函数。

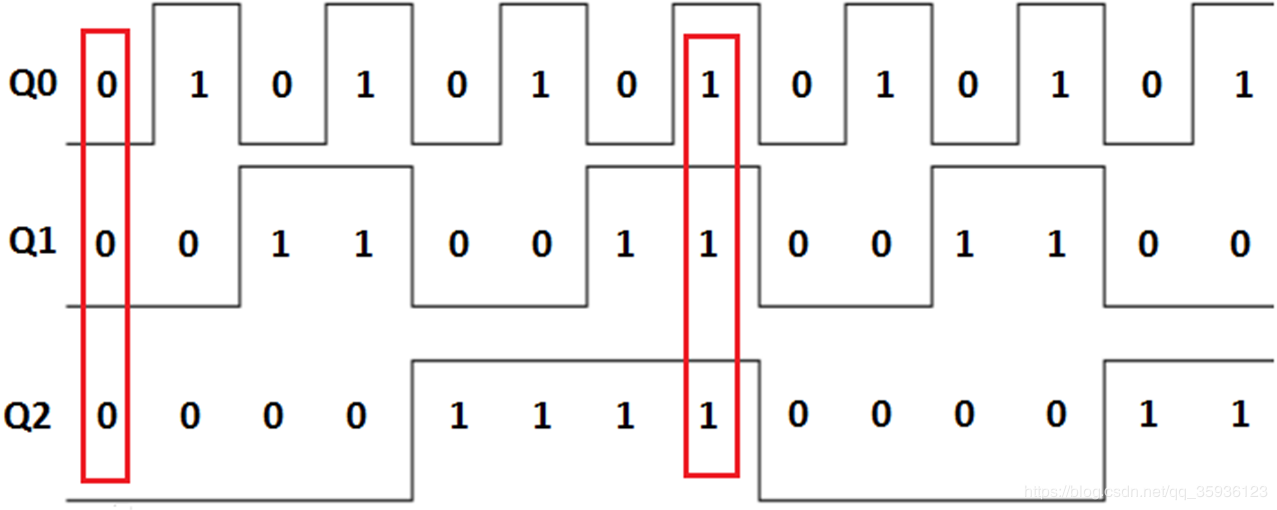

时序逻辑电路中最重要的一种电路类型是计数器,其主要功能是对输入时钟脉冲的个数进行计数。假设一个3位的二进制计数器[Q0, Q1, Q2],其计数范围000~111,在输入时钟脉冲CP的驱动下,其状态是:000、001、010、…110、111。如下图1所示,把Q0、Q1和Q2端的波形沿着时间轴排列对齐,可以看出计数器各位之间是分频关系:Q1端是低位Q0端的二分频,Q2端是低位Q1端的二分频及Q0端的四分频。类似地,在n位二进制计数器[Q0…Qn]中,任意Qn端都是相邻低位Qn-1端的二分频。因此,一方面计数器可以作为分频器使用,另一方面计数器的设计亦可以参考下图1中计数器各位信号的波形。

图1:3位二进制计数器的输出波形示意图

图1

异步/同步计数器

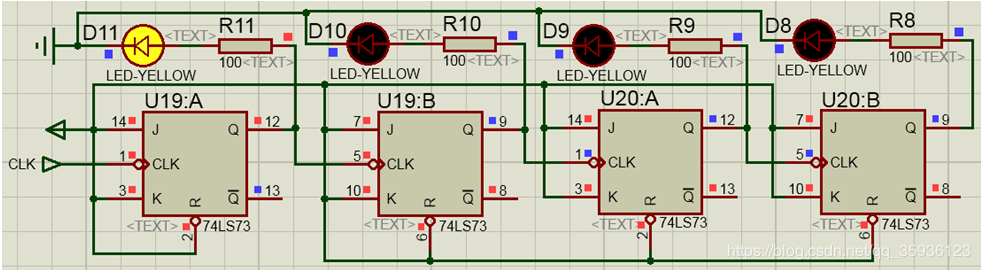

如上图1所示,计数器的每个位输出波形都是方波,即“0”、“1”电平交替,电平间隔时间相同。所以,计数器每个位的输出信号很容易用一个JK触发器来产生。同时,因为每个位的输出波形是相邻低位波形的二分频,故可用相邻低位的JK触发器输出作为本位JK触发器的时钟源,使得相邻低位信号状态边沿跳变(例如下降沿)时刻,本位信号状态翻转。因为该类型的计数器中所有位的JK触发器时钟源不是同一个时钟源,所以称为异步计数器。一个基于JK触发器的4位异步加法计数器如下图2所示。

图2. 异步计数器的时序逻辑电路

图2

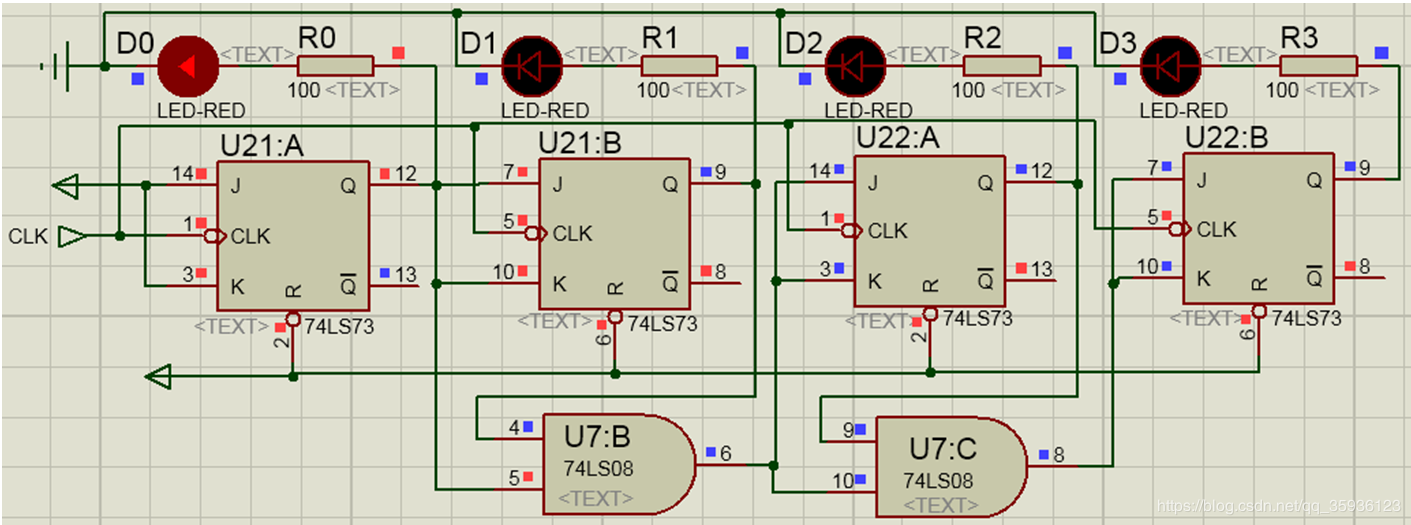

计数器的另一种更常见的结构设计是同步计数器,如下图3所示:所有位的JK触发器都由同一时钟源CLK驱动。在同步计数器中,每一位JK触发器的状态翻转由J和K端的当前状态决定;“当所有低位全1时,本位触发器的J=K=1”。因此,在下图3所示的4位同步计数器[D0,D1,D2,D3]中,D1位翻转的条件是D0=1,D2位翻转的条件是D0=D1=1(与门实现),而D3位翻转的条件则是D2=D1=D0=1(两个与门级联实现)。

图3. 同步计数器的时序逻辑电路

图3

加法/减法计数器

上述异步和同步计数器电路皆默认在时钟信号CLK的驱动下,计数器的输出是递增的,即加法计数器。在实际应用中,亦有可能需要计数器的输出是递减的,即减法计数器。

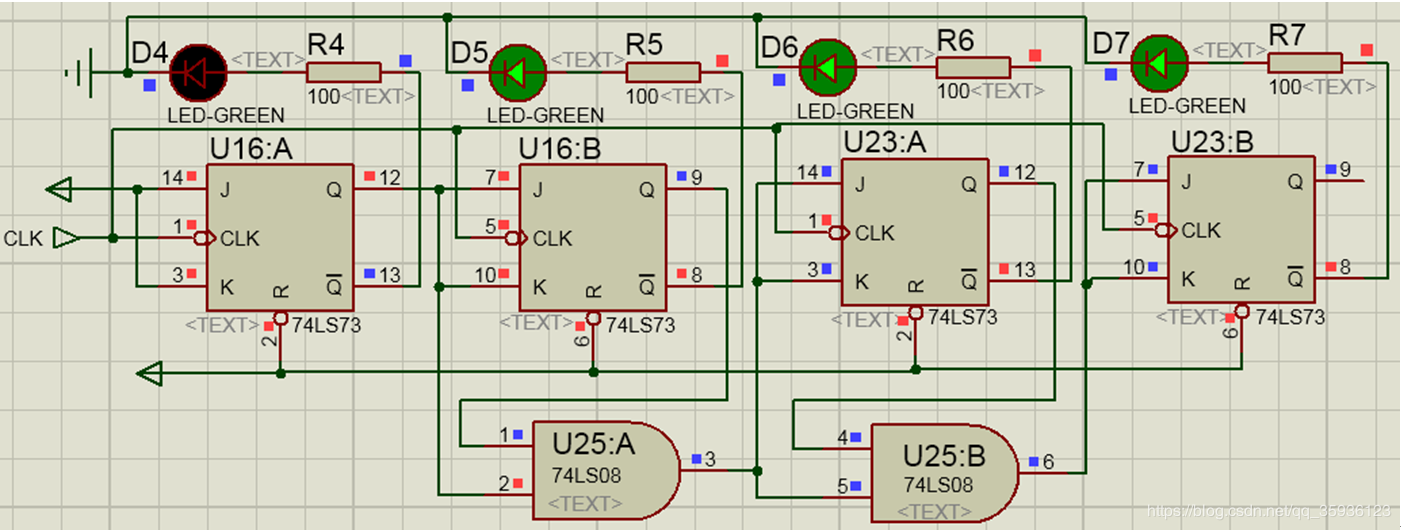

减法计数器最简单的构造方法是把加法计数器的输出反向,即加法计数器递增操作“+1=-(-1)”,加法计数器正向输出端[D0,D1,D2,D3]递增,对于其反向输出端[#D0, #D1, #D2, #D3]则是递减。因此,如下图4所示的同步减法计数器电路与上图3所示的同步加法计数器电路完全相同,唯有输出端是JK触发器的反向输出端#Q,而同步加法计数器输出端是JK触发器的正向输出端Q)。

图4. 同步减法计数器的时序逻辑电路

图4

任意进制计数器

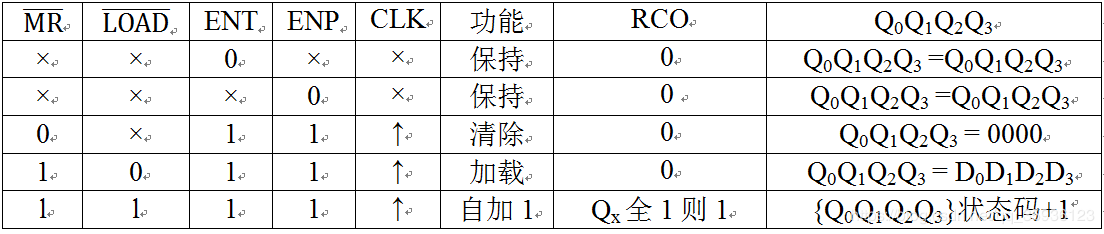

在集成电路中,除了二进制计数器以外,还有其它进制计数器需求,例如统计显示常用的10进制、时钟显示的60进制、24进制等等。10进制计数器有专用的集成电路器件74LS160,除了表数范围0000 ~ 0001与二进制计数器74LS163的表数范围0000 ~ 1111不同以外,74LS160的逻辑功能与74LS163完全相同,如下表1所示。

表1. 同步计数器74LS163/74LS160真值表

表1

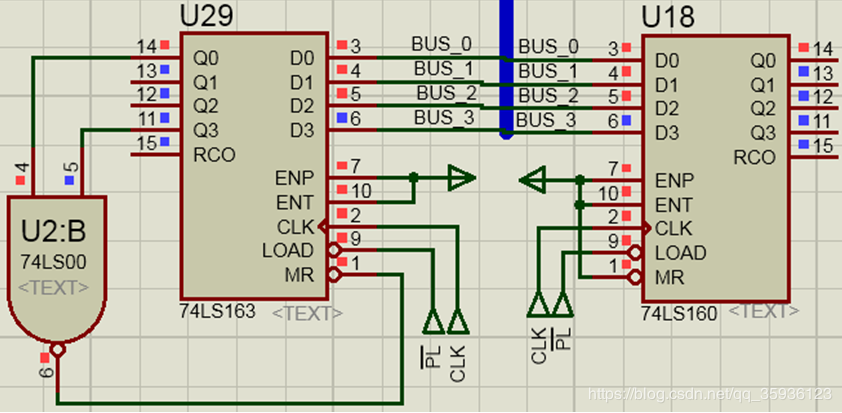

而其它任意n进制的计数器均可以基于74LS163增加清零电路构造,例如下图5所示:BUS总线右边是十进制计数器74LS160电路,而BUS总线左边则是基于二进制计数器74LS163的电路。BUS总线两边电路实现的功能完全等效:当74LS163的计数值到“1001”后,通过清零电路(与非门)置位清零端MR,CLK端的下一个上升沿跳变则令74LS163输出强制为0。因此,74LS163的表数范围限定于0000~1001(即10进制)。

图5 计数器74LS160及74LS163电路

图5

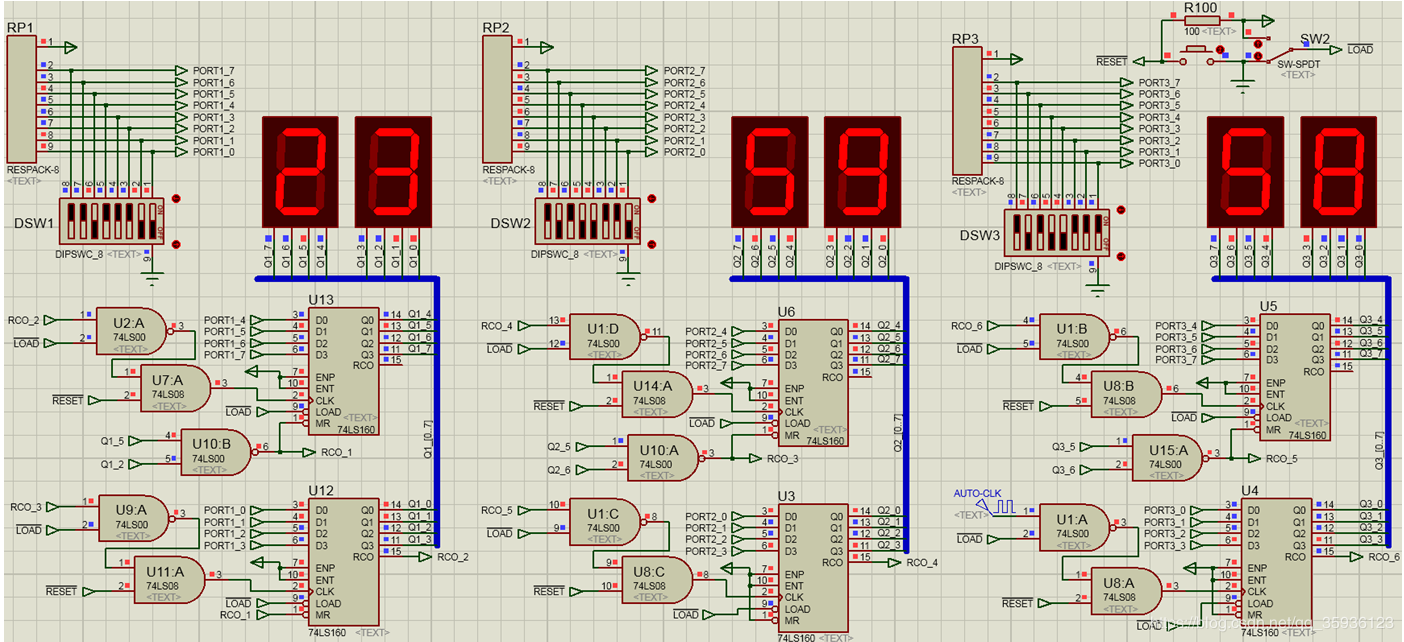

计数器设计示例:电子钟

下图6所示是一个经典的计数器设计示例:“时-分-秒”计时显示的电子钟。图中从左到右分别是电子钟的时钟、分钟和秒钟的计时单元,每个单元包括:2个10进制同步加法计数器74LS160分别计数十位和个位,对应的两个数码管显示十位和个位信息,而8位拨码开关用来给2个计数器置位。此外,秒钟电路上方是复位RESET电路,其操作方法如下:

1)若置位端#LOAD=0,电子钟处于加载模式:电子钟停止运行,便于重置计时初始值。此时,若手动按钮令信号#RESET 上升沿跳变,则拨码开关DSW1/DSW2/DSW3设置的计时初始值将加载到电子钟的时钟/分钟/秒钟单元,并且在数码管显示。启动仿真前,电子钟必须处于该模式,便于启动仿真后,先重置“时/分/秒”数据,再开始计时。

2)若置位端#LOAD=1,电子钟处于计数模式,开始倒计时。在该模式下,不允许手动按钮令信号#RESET变化,否则会出错。

图6 .电子钟电路图

图6

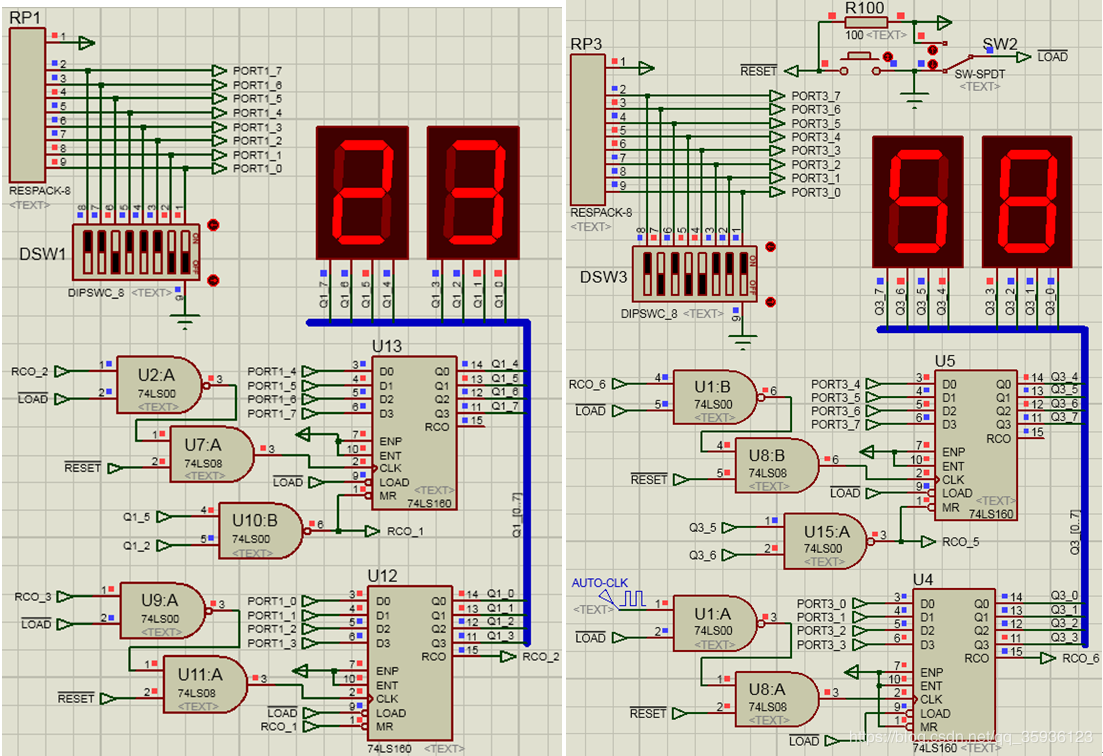

下图7所示是电子钟的时钟和秒钟计时单元电路(分钟电路与秒钟电路基本相同,省略不述),都是由两个10进制同步加法计数器74LS160级联组成的计数器。不同的是,图7(左)所示的时钟计时单元是24进制计数器电路,而图7(右)所示的秒钟/分钟计时单元则是60进制计数器电路。

当置位端#LOAD=0, 电子钟进入加载模式(初始化或重置):基准脉冲AUTO-CLK和所有的进位输出端RCO_x都被#LOAD信号屏蔽为“1”(即所有计数器停止计时),而所有计数单元的CLK输入端直接连到复位端#RESET。若在复位电路中手动按钮令使#RESET信号上跳沿跳变,将使时钟/分钟/秒钟计时单元的计数器输入端D0D1D2D3(连接8位拨码开关)同步置数到输出端Q0Q1Q2Q3,即计数器加载计时初始值成功。

当置位端#LOAD=1,电子钟进入计数模式:当低位计数器74LS163输出端Q3Q2Q1Q0全“1”时,进位输出端RCO=1送到高位计数器74LS163的ENT和ENP端,使得高位计数器74LS163在下一次的CLK上升沿自加1一次(同时RCO=0,所以仅一次自加1)。

图7. 电子钟的时钟和秒钟计时单元电路图

图7

参考资料

本文的内容节选自作者编撰的教材专著《基于Proteus的计算机系统实验教程——逻辑、组成原理、体系结构、微机接口》(机械工业出版社),更详细的内容可以直接在书中查阅。

读者如有兴趣,可以在 当当网图书, 京东图书,亚马逊上搜索作者姓名赖晓铮即可找到这本著作。

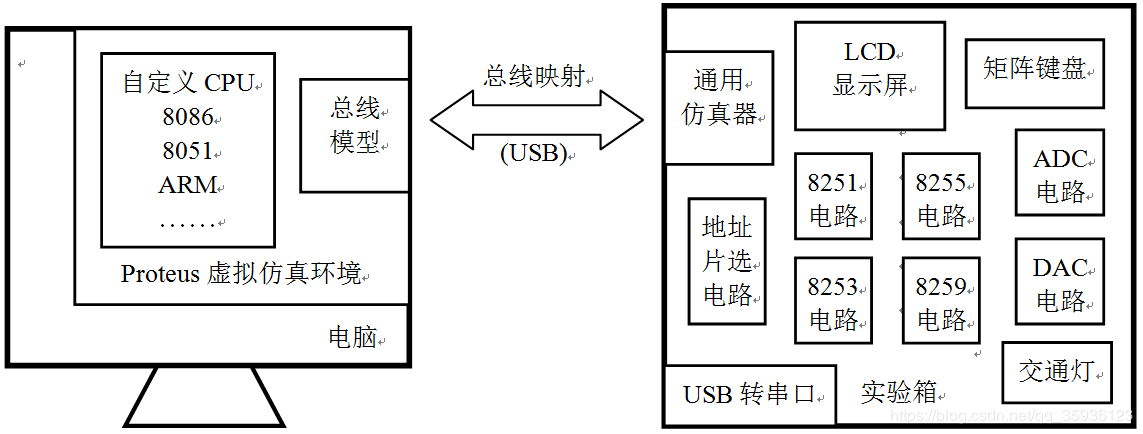

本书详细描述了在proteus虚拟仿真环境中,从逻辑电路开始,一步一步构造运算器、存储器、控制器,最终用三种CPU体系架构(微程序、硬布线、流水线)实现了一个8位的CPU。并且,这个CPU不仅可以做逻辑、算术运算,拥有循环、分支、堆栈等程序结构,还可以完整实现对8086所有外设的控制,即替代8086完整实现了传统《微机原理》里讲到的所有外设实验。

本书的全部proteus工程文件,PPT,实验视频以及配套的两种形式课程设计(纯汇编、硬件改动)的资料都放在百度网盘,提取密码:34ad

广州风标为本书配套了实验箱(如下图所示),可以让学生在电脑的proteus虚拟仿真环境中设计CPU或选择已有的8086、8051、ARM等CPU模型,然后通过虚拟总线映射到实验箱的物理总线,控制实验箱面板上的真实外设。有兴趣的读者可以自行联系广州风标教育技术股份有限公司。

作者:华南理工大学 赖晓铮教授

- 案例分享│浙江商业职业技术学院《智能电子产品设计与仿真》在线开放课程备受好评!

- 教材分享《数字逻辑与数字系统设计实验教程》

- 智能系统及其应用--毕盛

- 智能电子产品设计与制作

- 基于Proteus 和Keil 的C51 程序设计项目教程(第2版)——理论、仿真、实践相融合

- 2022年新书分享《基于Proteus的电路与PCB设计》

- Proteus推荐教材《嵌入式微控制器原理及设计——基于STM32及Proteus仿真开发》

- Proteus推荐教材《单片机原理与应用设计(C51编程 +Proteus仿真第3版高等学校规划教材)》

- Proteus 推荐教材《嵌入式处理器及物联网的可视化虚拟设计与仿真——基于Proteus》

- Proteus推荐教材《基于Proteus的电路与PCB设计》