基于proteus的一个硬布线CPU

指令集与CPU架构

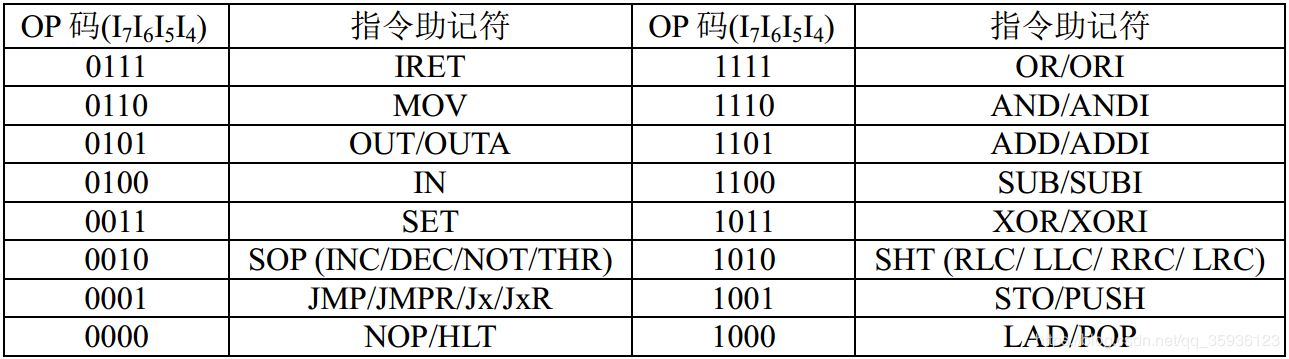

本文是前述文章基于proteus的一个微程序CPU的姐妹篇,硬布线CPU的指令集完全兼容微程序CPU的指令集,分为以下五大类共38条机器指令,指令OP码如下表1所示:

1)系统指令:NOP、HLT、IRET;

2)寄存器及I/O操作指令:MOV、SET、IN、OUT/OUTA;

3)存储器及堆栈操作指令:LAD/POP、STO/PUSH;

4)跳转系列指令:JMP、JMPR、Jx(JC/JZ/JS)、JxR(JCR/JZR/JSR);

5)算术逻辑运算指令:SHT (RLC/ LLC/ RRC/ LRC)、SOP (INC/DEC/NOT/THR)、ADD/ADDI、SUB/SUBI、AND/ANDI、OR/ORI、XOR/XORI;

表1. 硬布线CPU指令集

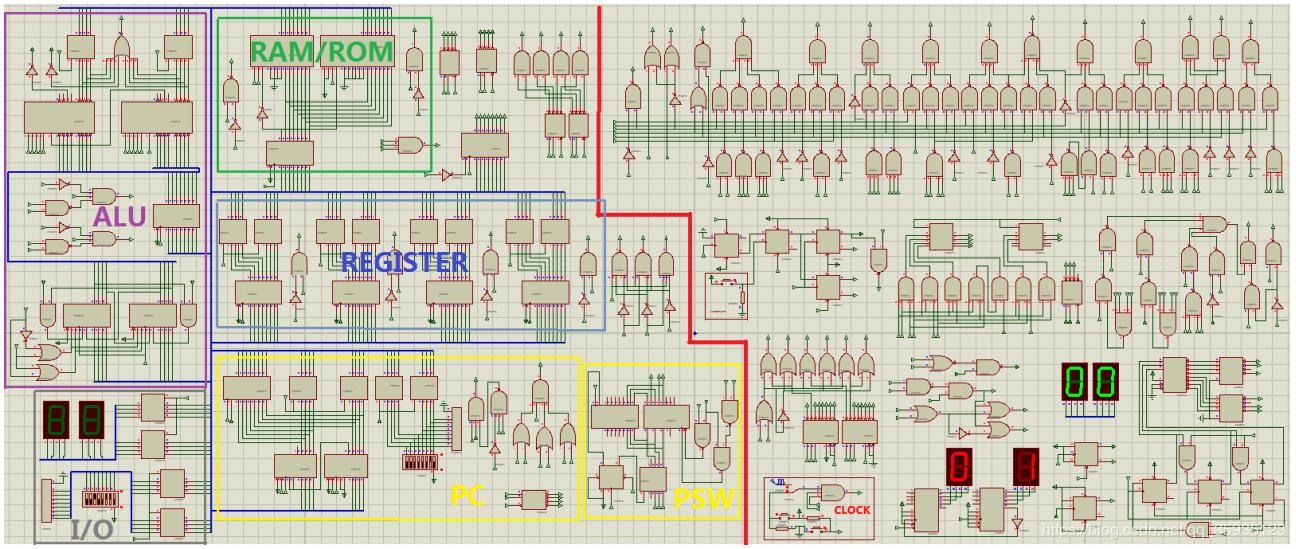

硬布线CPU电路图如下图1所示,红线的左侧是与微程序CPU完全兼容的数据通路,包括了:程序/数据存储器ROM/RAM及其地址寄存器AR;指令寄存器IR;通用寄存器R0~R3;算术逻辑运算器ALU及其附属缓存器DA(兼作移位功能)和DB;外设I/O接口;中断向量地址IVA;程序计数器(PC)、运算结果标志位寄存器(PSW)及其断点寄存器(BP_PC、BP_PSW)。而图1红线右侧则是与微程序控制器功能对应的硬布线控制器(包括基于两级状态机的时序发生器电路)以及中断电路。

图1. 硬布线CPU电路图

硬布线控制器

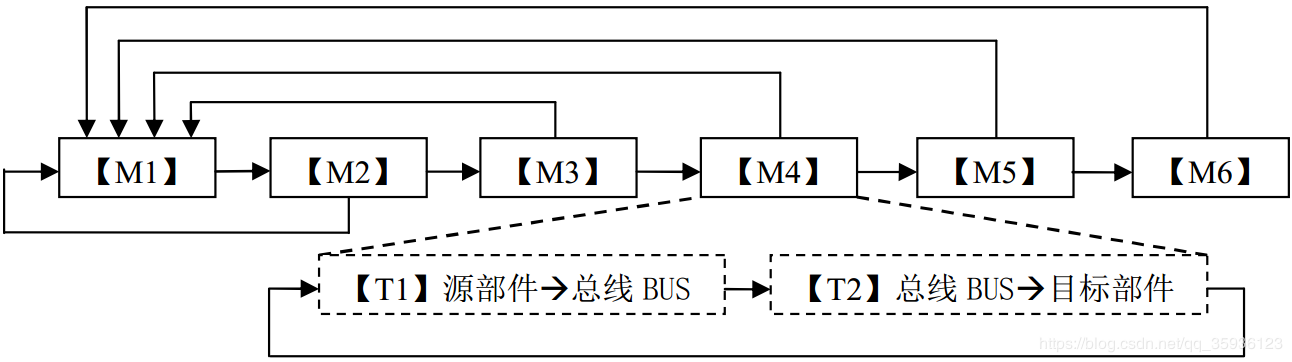

硬布线CPU的控制器属于多周期硬布线控制器,采用两级状态机架构,如下图2所示:一级状态机MCLOCK由六个状态{M1, M2, M3, M4, M5, M6}组成,其中M1-M2是取指状态,M3-M6是执行状态。每一次状态M循环对应一个指令周期,其状态数目不固定,由该指令决定。状态机在每条指令最后的执行状态Mx结束后,自动跳转到下一条指令的取指状态M1。每一个状态M本身是一个二级状态机,与微程序CPU的微指令状态机完全相同:包括两个状态{T1,T2},循环进行状态转移T1→T2。在T1状态,指令/数据先从源部件打入总线BUS;在T2状态,指令/数据再从总线BUS打入目标部件。

图2. 硬布线CPU控制器的状态机架构

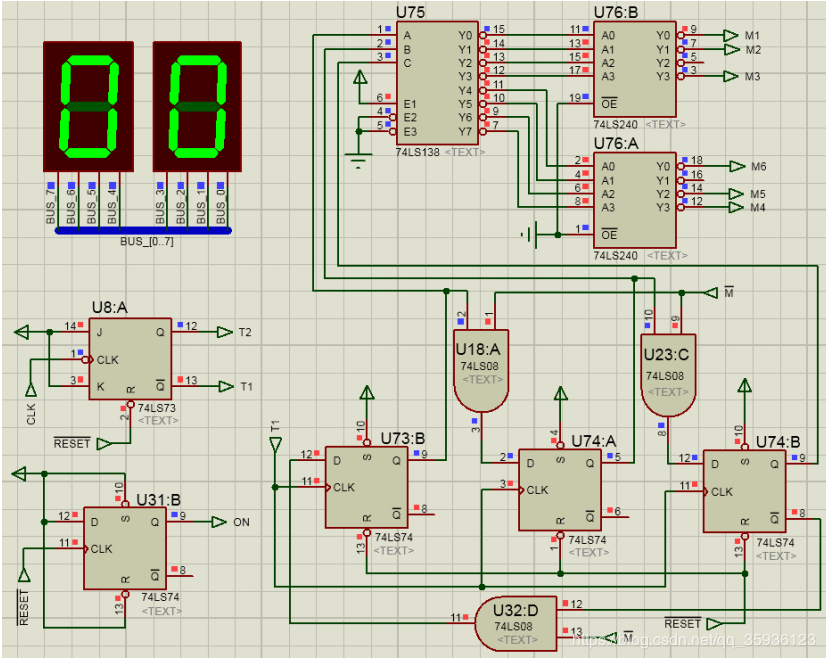

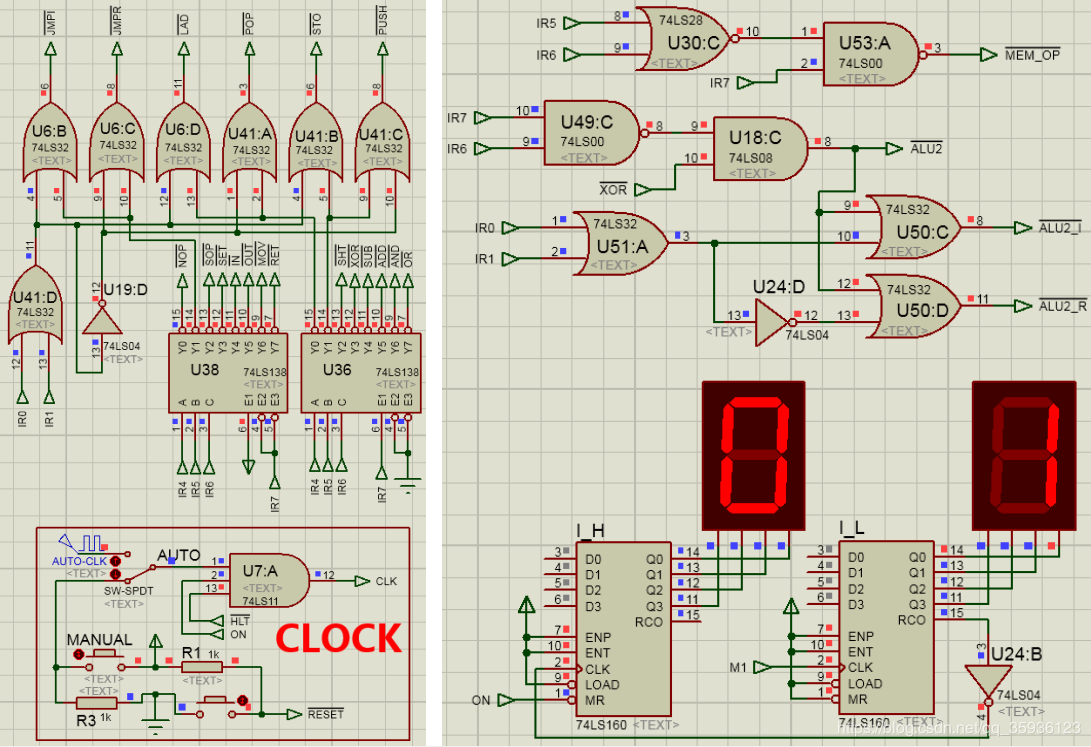

上述两级状态机的时序发生器电路如下图3所示,二级状态机与微程序CPU的微指令状态机完全相同,依旧使用JK触发器74LS73。时钟信号CLK驱动,循环进行固定的状态转移T1→T2。一级状态机则使用一个2位扭环计数器及其译码电路,由每次状态T循环开始的T1上升沿驱动,进行状态数量不固定的状态M循环(如图2所示)。一级状态机的次态Mx+1不仅取决于当前状态Mx,还由跳转信号#M决定:#M=1则照常进行状态转移Mx→Mx+1;#M=0则计数器输入置位{1,0,0,0},使次态Mx+1强制转移到M1。

图3. 状态机的时序发生器电路

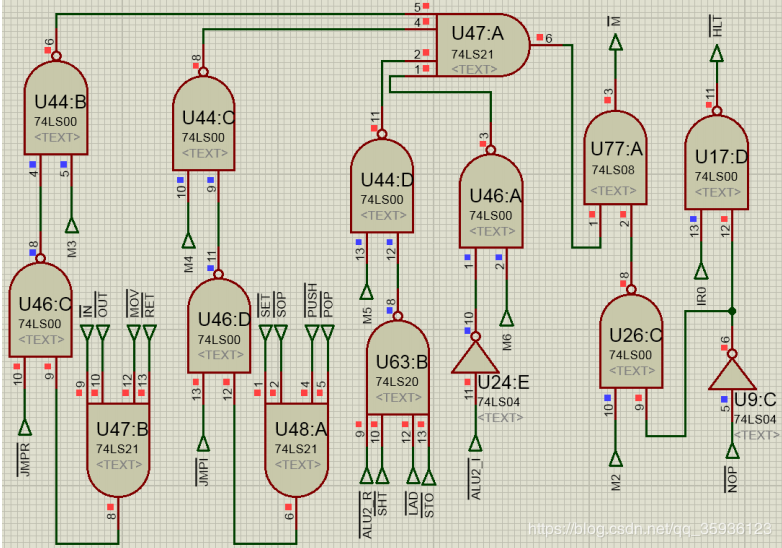

跳转信号#M的形成逻辑电路如下图4所示:当一条指令的当前状态是指令周期最后一个状态Mx,其指令信号与状态节拍信号Mx的逻辑“与”令跳转信号#M=0,从而使次态强制转移到下一条指令的取指状态M1,构成M1→Mx循环。Mx与指令的关系如下:

Mx=M2 (M1→M2):NOP/HLT指令

(注:如下图4所示,#HLT指令信号由NOP指令产生,立即停机在状态M2的T2节拍)

2)Mx=M3 (M1→M3):IN、OUT、MOV、IRET、JMPR (JMPR/JxR) 指令

3)Mx=M4 (M1→M4):PUSH、POP、SET、SOP、JMPI (JMP/Jx) 指令

4)Mx=M5 (M1→M5):LAD、STO、SHT、ALU2_R (ADD、SUB、AND、OR、XOR) 指令

5)Mx=M6 (M1→M6):ALU2_I (ADDI、SUBI、ANDI、ORI、XORI) 指令

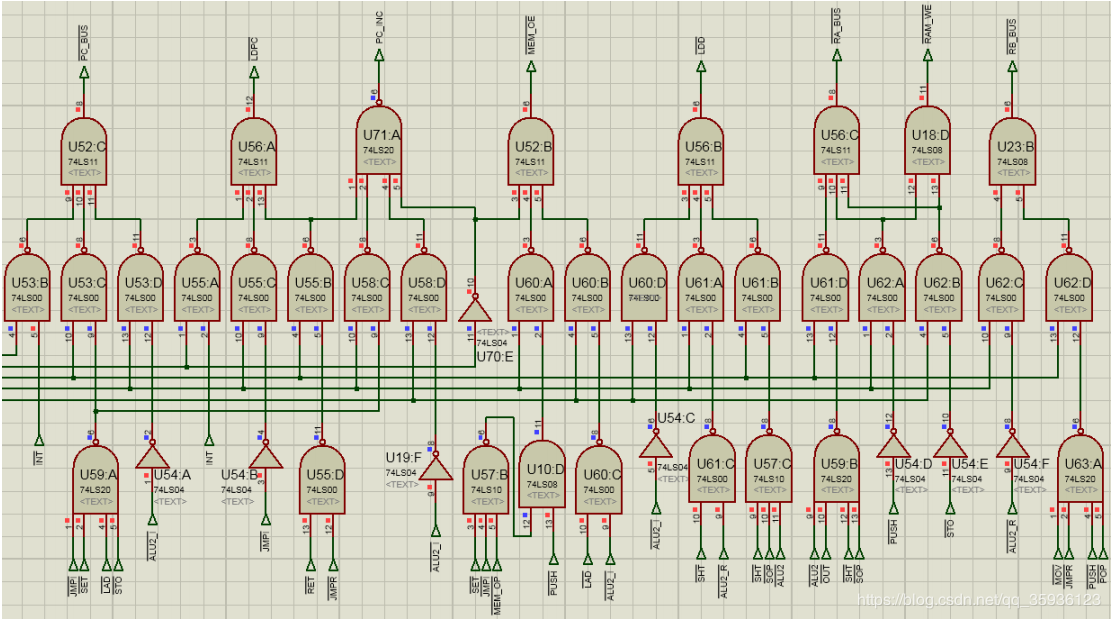

图4. 状态机的跳转信号形成逻辑电路

如下图5所示, 硬布线CPU是由指令寄存器IR保存的OP码{I7,I6,I5,I4}(参考上述CPU指令集列表1)经过两个74LS138译码器直接产生相应的指令信号。其中,单独设置指示信号ALU2代表五个双操作数运算指令ADD/SUB/AND/OR/XOR(这些指令状态机的时序相近),并且与指令寄存器IR的{I1I0}位结合,构成了以下两个指示信号:操作数之一来自指令第二字节IMM(立即数)的双操作数运算指示信号#ALU2_I和操作数全部来自寄存器的双操作数运算指示信号#ALU2_R。

另一方面,因为状态机时序相近的原因,在下图5中设置指示信号MEM_OP代表四个存储器操作指令LAD/STO/POP/PUSH。相似的,因为LAD/POP指令、STO/PUSH指令和跳转系列指令共用OP码,所以需要{I1,I0}位参与指令译码:当I1I0=00时,生成跳转指令信号#JMP和存储器操作指令信号#LAD/#STO(跳转目标地址或操作数地址来自指令第二字节ADDR);当{I1,I0}≠00时,生成跳转指令信号#JMPR和堆栈操作信号#POP/#PUSH(跳转目标地址或操作数地址来自寄存器)。

图5. 指令译码电路

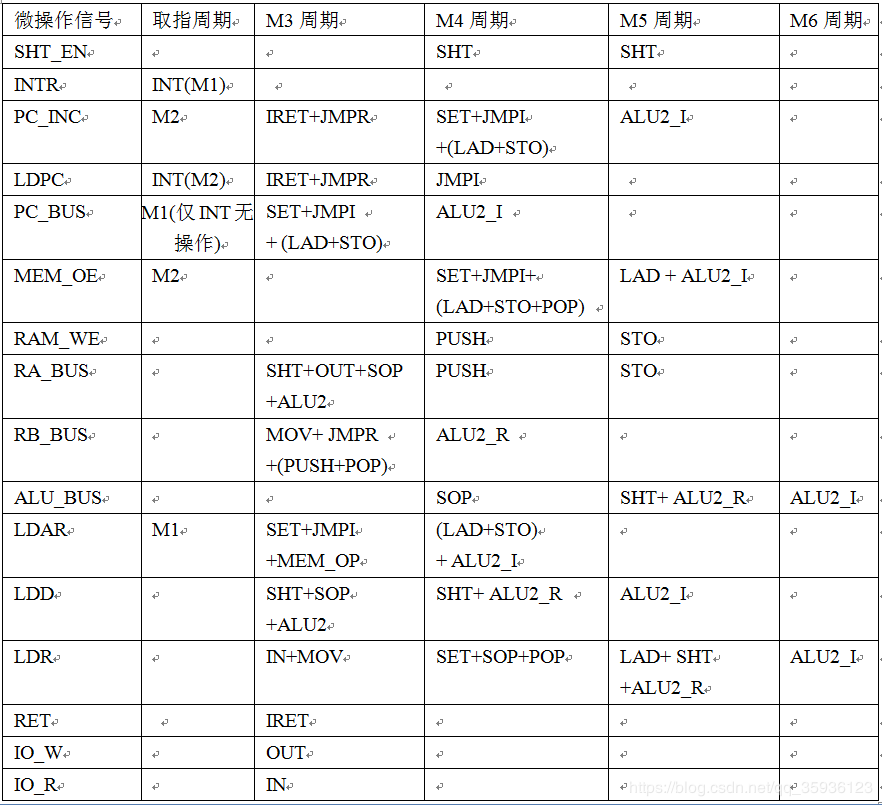

因为数据通路是相同的,所以硬布线CPU执行指令所需的微操作信号序列与前述微程序CPU保持一致。每一个微操作信号由当前状态节拍信号Mx和特定的指令信号通过逻辑与形成。如下表2所示。

表2. 微操作信号形成逻辑

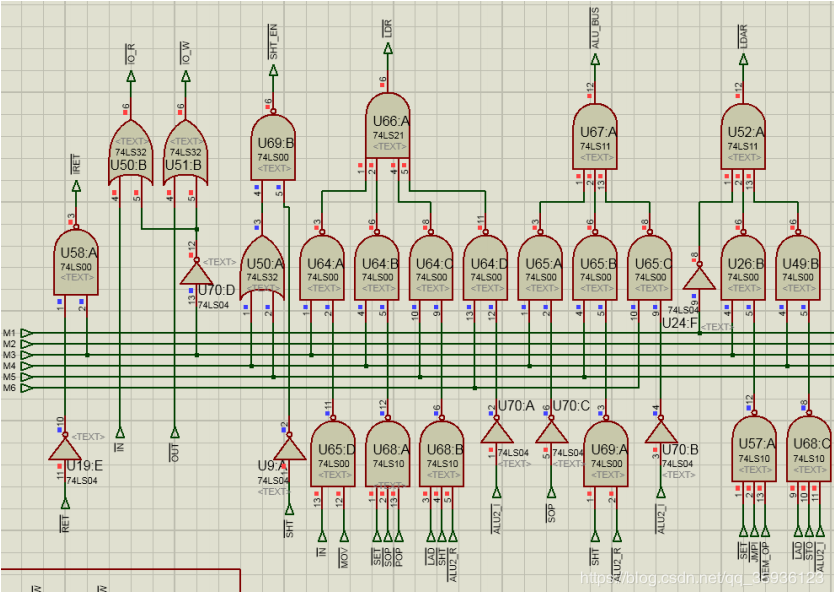

根据上表2可以推导出如下图6所示的微操作信号硬布线逻辑电路。其中,横向信号线是状态节拍信号Mx(M1~M6),横向信号线下方是指令寄存器IR译码生成的指令信号组合。横向信号线上方的一排与非门和反相器则对应上表2的所有方框:每个与非门的一端输入横向信号线下方的指令信号组合(对应上表2某个方框中的所有指令信号)的逻辑或,另一端输入状态节拍信号Mx;每个反相器只输入节拍信号Mx(反相器),表示任何指令在该状态Mx都有效。在下图6中,最上方的若干个与非门或反相器输出(低电平有效)通过与门逻辑形成某一个微操作信号(对应上表2中的某一行)。

图6. 微操作信号硬布线逻辑电路

指令流程图

硬布线CPU的状态机流程图与微程序CPU的微程序流程图基本相同,其中每一个方框代表一个状态Mx,对应微程序流程图中的一条微指令。每一个方框内的微操作信号都由上图6所示的硬布线逻辑电路生成,亦与微程序流程图方框中的微操作信号基本一致。

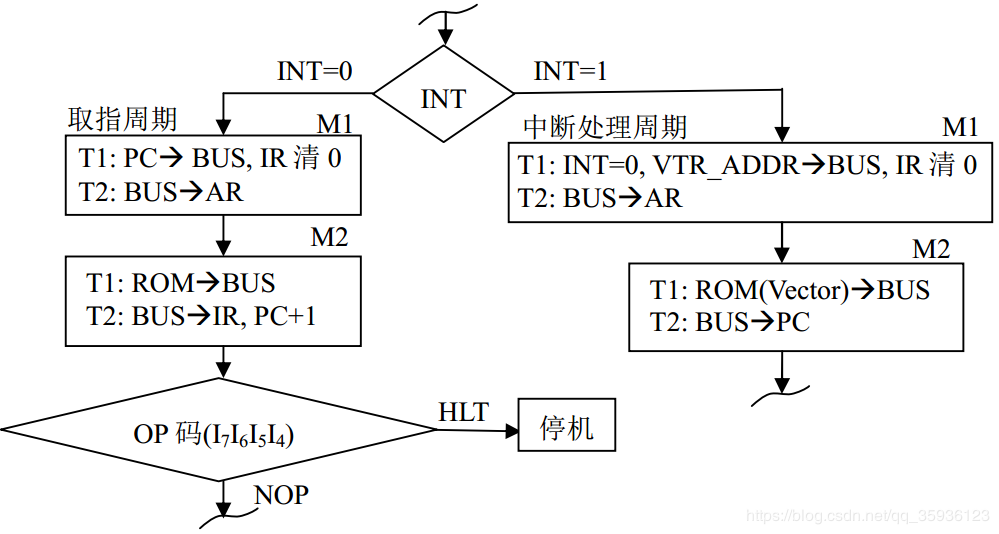

取指周期和中断处理周期的状态机流程图如下图7所示:所有机器指令至少需要2个CPU周期(M1和M2)的取指周期,在M1周期开始时刻,通过中断标记信号INT决定是运行取指周期(INT=0),还是运行中断处理周期(INT=1)。指令寄存器IR在M1周期或者复位信号#RESET=0的情况下清零。在取指周期M2的T2节拍上升沿时刻,信号IR_CLK上跳变,把从程序存储器PROGRAM取出的指令打入指令寄存器IR,再通过指令寄存器IR的{I7,I6,I5,I4}译码产生一系列的指令信号(如上述指令译码电路图5所示)。若产生NOP指令信号,则直接返回M1周期取出下一条指令;若产生HLT指令信号,则CPU直接停机,重启跳出断点后进入下一指令的取指周期。若产生其他信号,则进入执行周期(M3~M6)。

图7. 取指周期和中断处理周期的状态机流程图

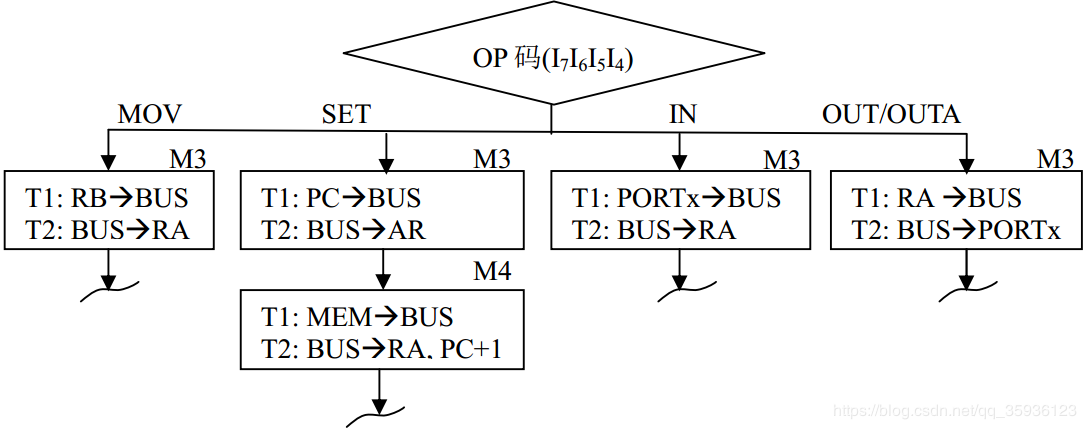

如上图7 所示,所有CPU指令的状态机都经过公共的取指周期(M1~M2状态),然后在取指周期末尾,OP码{I7,I6,I5,I4}译码产生一系列指令信号,进入各自指令的执行周期。下图8列出了寄存器操作指令(MOV、SET指令)和I/O操作指令(IN、OUT/OUTA指令)执行周期的状态机流程图,与微程序流程图完全一致。

图8. 寄存器及I/O操作指令的状态机流程图

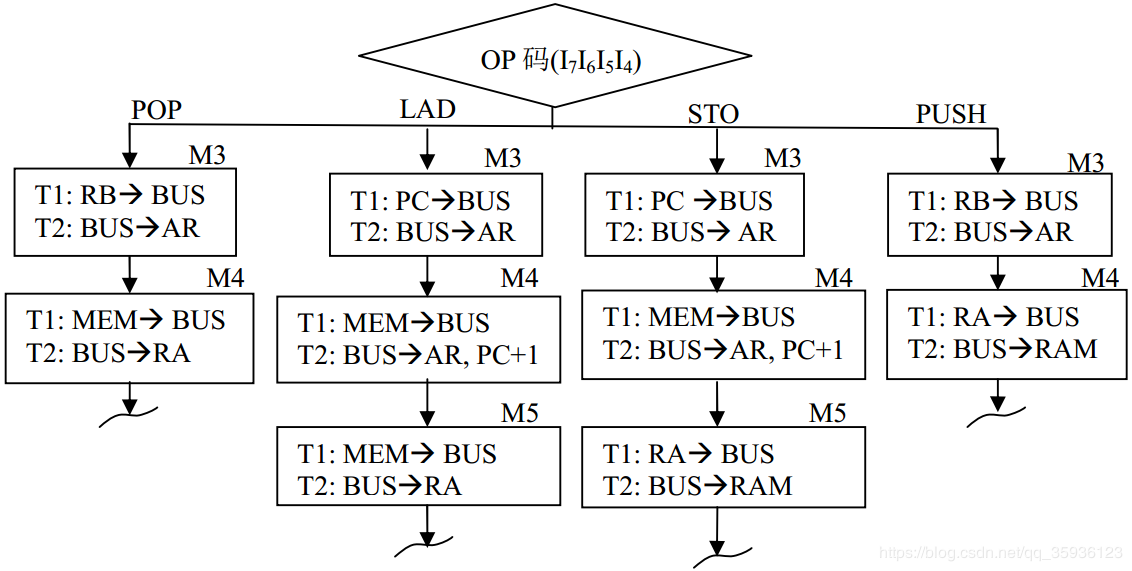

下图9列出存储器操作指令(LAD/STO指令)和堆栈操作指令(POP/PUSH指令)执行周期的状态机流程图。与微程序流程图相比,硬布线版本CPU不需要考虑微指令容量问题,因此堆栈操作指令POP和PUSH的执行周期只占用两个CPU周期,效率得到提升。

图9. 存储器及堆栈操作指令的状态机流程图

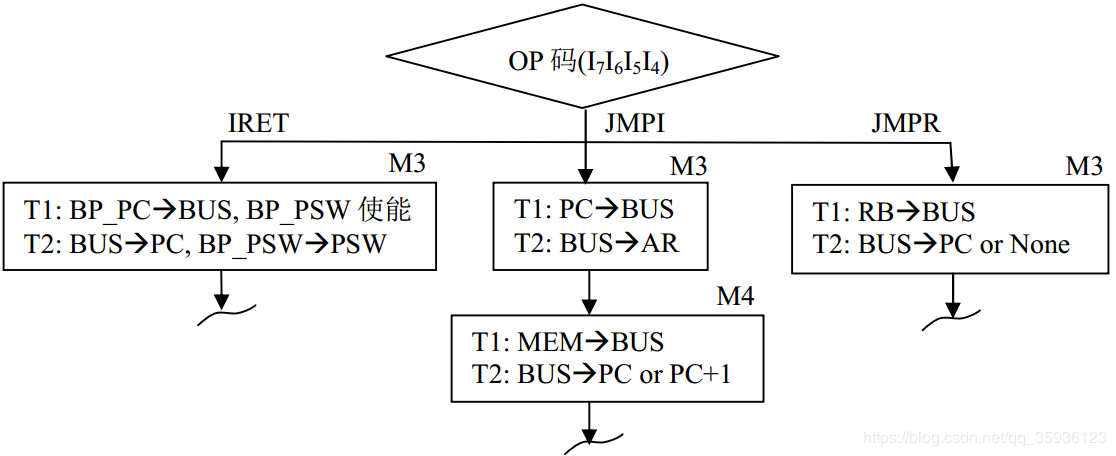

下图10所示的状态机流程图包括了中断返回指令、目标地址来源寄存器的跳转指令JMPR(包括JMPR和JxR系列指令)和目标地址来源存储器的跳转指令JMPI(包括JMP和Jx系列指令)。与微程序流程图相比,硬布线版本CPU不需要考虑微指令容量的问题,因此跳转指令JMPR的执行周期只占用两个CPU周期,效率大大提高。

图10. 中断返回及跳转系列指令的状态机流程图

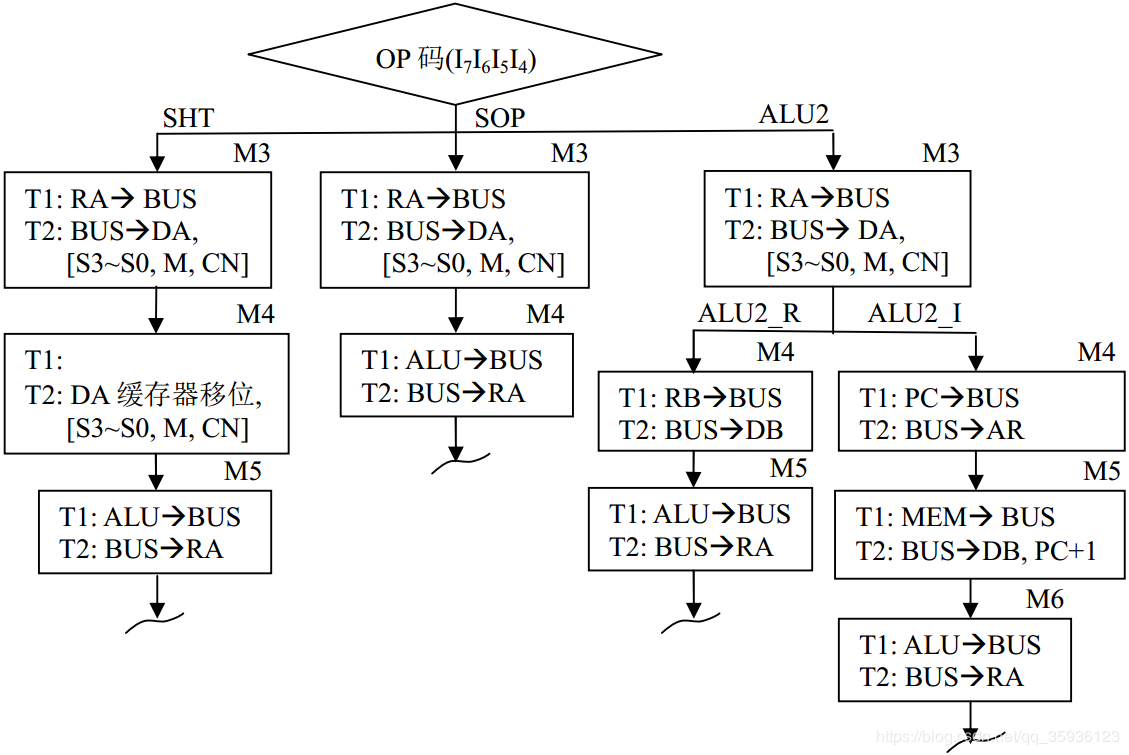

如下图11所示:算术逻辑运算系列指令的状态机都在M3周期生成运算器74LS181的控制端逻辑[S3,S2,S1,S0,M,CN],其中,双操作数运算指令ALU2系列(包括ADD、SUB、AND、OR、XOR五种指令)在M3周期微操作信号一致,在M4周期则出现两个分支:操作数之一来自存储器的指令系列ALU2_I和操作数全部来自寄存器的指令系列ALU2_R。

图11. 算术逻辑运算系列指令的状态机流程图

参考资料

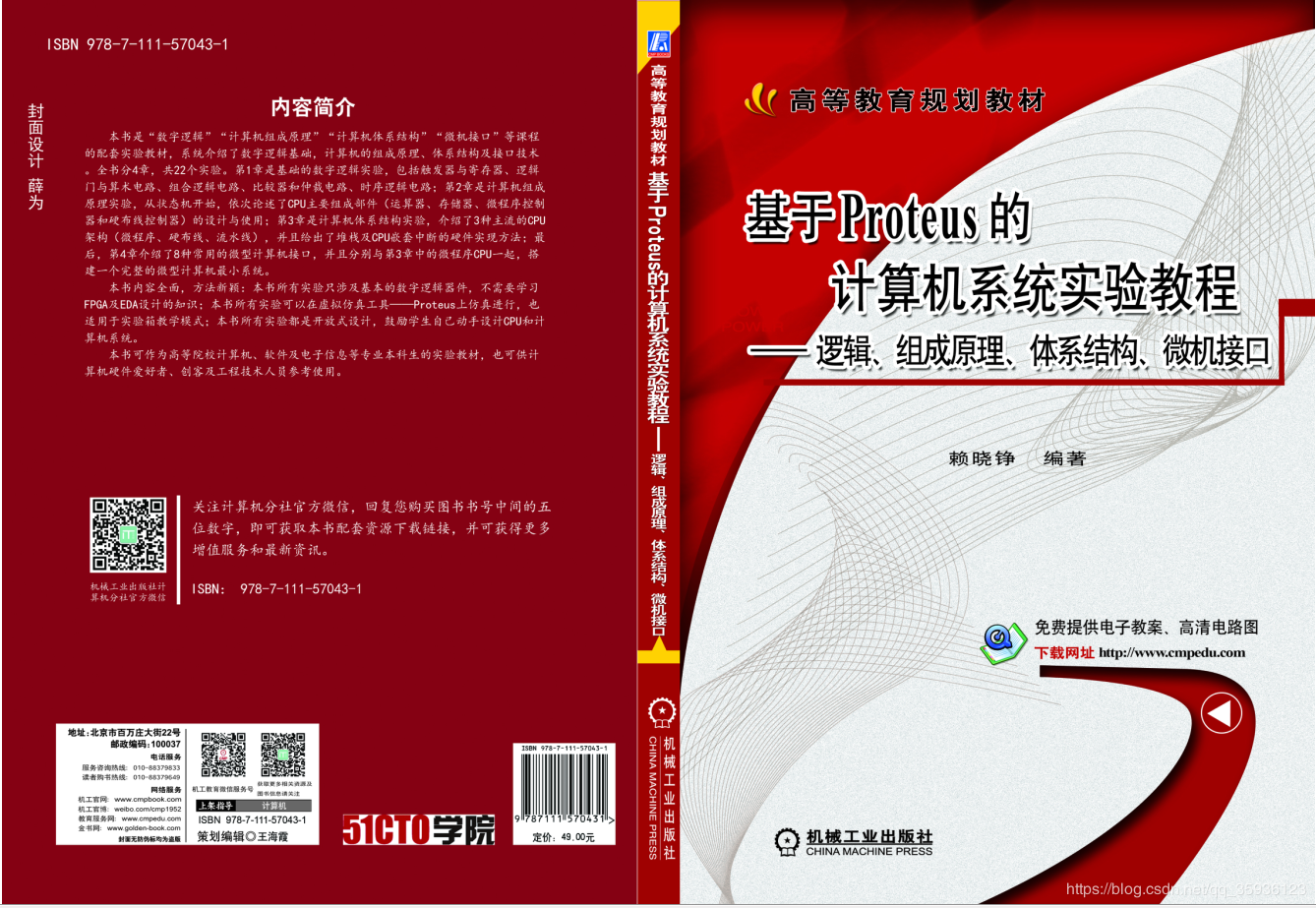

本文的内容节选自作者编撰的教材专著《基于Proteus的计算机系统实验教程——逻辑、组成原理、体系结构、微机接口》(机械工业出版社),更详细的内容可以直接在书中查阅。

读者如有兴趣,可以在当当网图书, 京东图书,亚马逊上 搜索作者姓名赖晓铮即可找到这本著作。

本书详细描述了在proteus虚拟仿真环境中,从逻辑电路开始,一步一步构造运算器、存储器、控制器,最终用三种CPU体系架构(微程序、硬布线、流水线)实现了一个8位的CPU。并且,这个CPU不仅可以做逻辑、算术运算,拥有循环、分支、堆栈等程序结构,还可以完整实现对8086所有外设的控制,即替代8086完整实现了传统《微机原理》里讲到的所有外设实验。

本书的全部proteus工程文件,PPT,实验视频以及配套的两种形式课程设计(纯汇编、硬件改动)的资料都放在 百度网盘,提取密码:34ad

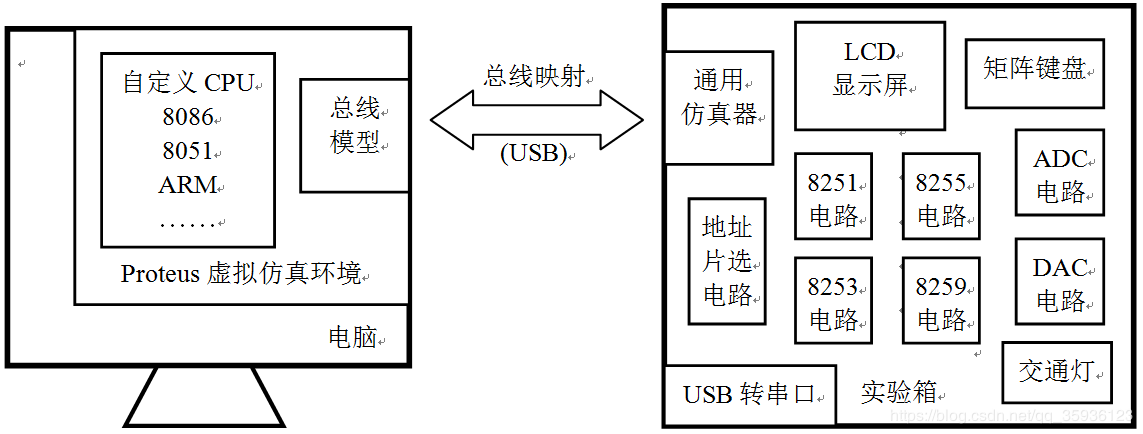

广州风标为本书配套了实验箱(如下图所示),可以让学生在电脑的proteus虚拟仿真环境中设计CPU或选择已有的8086、8051、ARM等CPU模型,然后通过虚拟总线映射到实验箱的物理总线,控制实验箱面板上的真实外设。有兴趣的读者可以自行联系 广州风标教育技术股份有限公司。

作者:华南理工大学 赖晓铮教授

- 案例分享│浙江商业职业技术学院《智能电子产品设计与仿真》在线开放课程备受好评!

- 教材分享《数字逻辑与数字系统设计实验教程》

- 智能系统及其应用--毕盛

- 智能电子产品设计与制作

- 基于Proteus 和Keil 的C51 程序设计项目教程(第2版)——理论、仿真、实践相融合

- 2022年新书分享《基于Proteus的电路与PCB设计》

- Proteus推荐教材《嵌入式微控制器原理及设计——基于STM32及Proteus仿真开发》

- Proteus推荐教材《单片机原理与应用设计(C51编程 +Proteus仿真第3版高等学校规划教材)》

- Proteus 推荐教材《嵌入式处理器及物联网的可视化虚拟设计与仿真——基于Proteus》

- Proteus推荐教材《基于Proteus的电路与PCB设计》